## 35 GHz InGaAs HEMT MMIC Downconverter

J. Yonaki, R. Carandang, B.A. Allen, M. Hoppe, W.L. Jones,

D.C. Yang, and C.L. Brunnenmeyer

TRW/ESG Electronics and Technology Division

One Space Park

Redondo Beach, CA 90278

### ABSTRACT

The design and development of a 35 GHz HEMT MMIC downconverter is reported. This completely monolithic chip consists of a balanced two-stage low noise amplifier cascaded with a singly balanced (HEMT compatible) diode mixer. Conversion gain of 5 dB over a 20 to 100 MHz IF output with an RF frequency of 35 GHz and an LO frequency = RF + IF has been measured. In addition to the downconverter macrocell, the LNA and mixer designs were fabricated as individual microcells. The LNA has demonstrated state-of-the-art performance: measured noise figure (NF) from 34 to 40 GHz is less than 2.8 dB. Associated gain is 14.0 +/- 0.4 dB over a 30 to 40 GHz bandwidth. Input and output VSWR is better than 1.2 : 1. The singly balanced mixer exhibited conversion loss of less than 5 dB. The design and test results of these circuits are presented.

### INTRODUCTION

Lower cost and higher performance millimeter-wave radar and communication systems can be realized most efficiently through higher levels of monolithic integration. Monolithic implementation reduces cost, size, and weight of receiver components while integration of multiple functions improves performance and reliability by reducing the number of parasitic wire bonds.

Recent advances in multi-function MMIC chips [1,2,3] have been reported. In this paper, we

describe the development of a fully integrated 35 GHz HEMT MMIC downconverter which exhibits state-of-the-art performance.

### LNA DESIGN

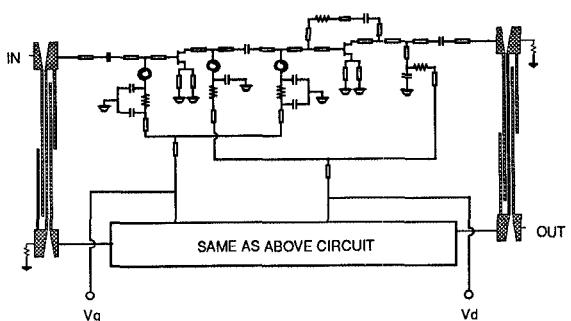

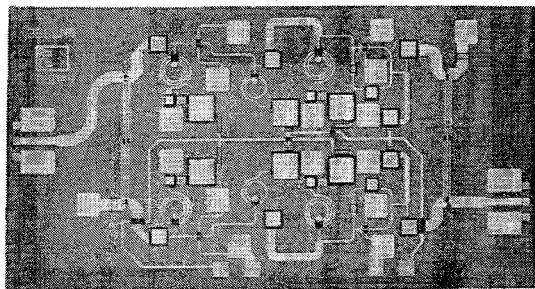

In order to achieve optimum noise performance along with favorable input and output VSWR, a balanced topology using Lange couplers was implemented. The individual (single-ended) two-stage amplifiers utilize series feedback on the first stage for improved stability and shunt feedback on the second stage for flat gain over the 30 to 40 GHz band. Both stages use  $0.2 \times 100$   $\mu\text{m}$  interdigitated (four finger) InGaAs HEMTs for the best combination of NF and gain. The balanced LNA is realized by embedding two identical two-stage LNAs in a pair of Lange couplers which provide excellent input and output match. The LNA circuit schematic and layout are shown in Figures 1 and 2. The balanced two-stage LNA chip measures 3.4 x 1.8 mm.

Figure 1. LNA Circuit Schematic

**Figure 2. LNA Chip Photo**

For improved process tolerance, the two stages were optimized with compensating gain slopes. Due to noise matching in the input stage, a negative gain slope exists. By designing the second stage with a positive gain slope, the overall amplifier gain remains relatively constant in spite of a wide range of process variations.

In order to simplify biasing of the LNA, the respective gate and drain paths of each of the four HEMTs are tied together. All four active devices are designed to operate under  $G_m$  peak conditions. To minimize chip size, spiral inductors are used to inject the DC bias. On-chip series resistors and bypass capacitors are incorporated into the biasing networks to ensure unconditional stability.

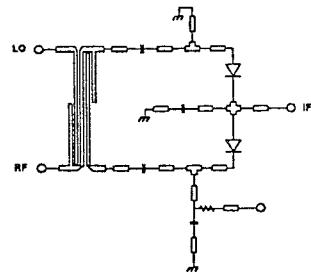

### MIXER DESIGN

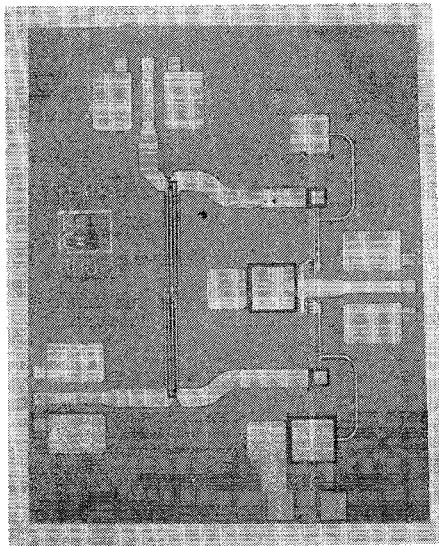

The singly balanced mixer is constructed with a Lange coupler, a pair of Schottky diodes, and bandpass matching networks. The Lange is used to inject the RF and LO signals and the gate finger Schottky barrier diodes are used as the mixing elements. The RF short and DC return path are realized by a shunt 3 pF capacitor and a grounded transmission line in the matching network, respectively. Each diode is constructed with a  $0.25 \times 10 \text{ }\mu\text{m} \times 4$  finger gate periphery and is compatible with our standard HEMT process. The

diode size was carefully chosen so that the impedance looking from the IF port was close to 50 ohms which reduced the IF matching network to a 50 ohm transmission line for the 0 to 100 MHz frequency range. To minimize assembly to external bias supplies, both diodes share the same bias pad. The mixer circuit schematic and chip photo are shown in Figures 3 and 4. The mixer microcell dimensions are  $1.51 \times 1.8 \text{ mm}$ .

**Figure 3. Mixer Circuit Schematic**

**Figure 4. Mixer Chip Photo**

### DOWNCONVERTER DESIGN

The downconverter macrocell was realized by cascading the balanced LNA with the singly balanced mixer onto a single monolithic chip.

Since both designs are matched to 50 ohms, a short section of 50 ohm transmission line was used to join the two circuits. The downconverter chip is shown in Figure 5 and measures 4.1 x 1.8 mm.

Figure 5. Downconverter Chip Photo

## MEASURED RESULTS

On-wafer measurements were made on the downconverter macrocell and the individual LNA and mixer microcells.

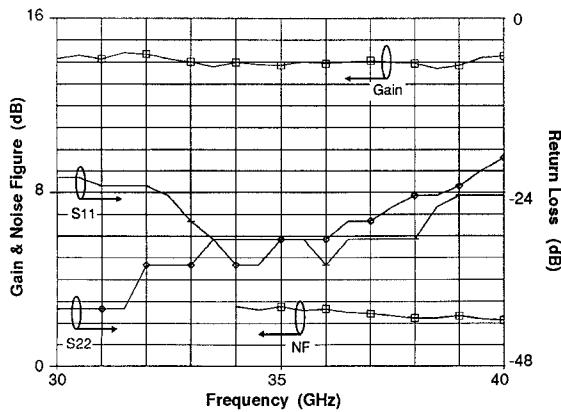

LNA. S-parameters over the 30 to 40 GHz bandwidth show a 14.0 dB gain with excellent flatness. Input and output return loss is greater than 20 dB. Noise figure from 34 to 40 GHz is < 2.8 dB (test equipment limitations prevented full band NF measurements). The LNA measured performance is shown in Figure 6.

Figure 6. Measured LNA Performance

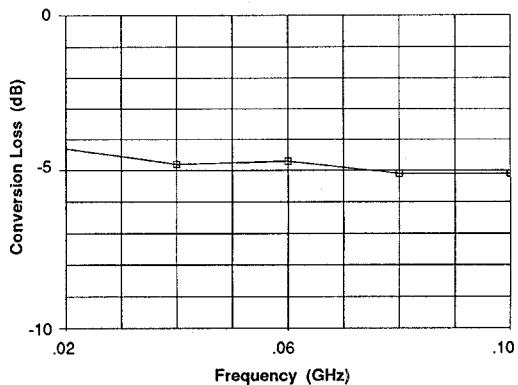

Mixer. With a 35 GHz RF signal and an LO = RF + IF, the IF conversion loss was < 5 dB over a 20 to 100 MHz output (Figure 7). The respective LO and RF drives were set to +10 dBm and -10 dBm due to system requirements. Figure 7 shows the measured mixer conversion loss.

Figure 7. Measured Mixer Performance

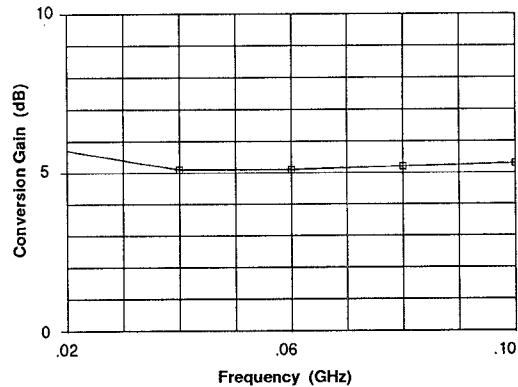

Downconverter. The downconverter macrocell's IF conversion measurements show gain > 5 dB over the 20 to 100 MHz output range. The downconverter measured gain is shown in Figure 8. NF and isolation measurements are to be scheduled.

Figure 8.

Measured Downconverter Performance

## CONCLUSION

Successful integration of a Ka-band LNA and HEMT compatible diode mixer to form a completely monolithic downconverter macrocell has been demonstrated. The LNA exhibits state-of-the-art performance and when combined with the low conversion loss of the mixer, has resulted in a downconverter macrocell with excellent overall performance. The performance achieved demonstrates the progress that is continuing to make affordable millimeter wave MMICs a reality.

## ACKNOWLEDGEMENTS

The authors would like to thank E. Archer and B. Nelson for their technical expertise, M. Iyama for layout, and F. Garcia and K. Wong for test.

This work was performed under the DARPA Microwave/Millimeter-wave Monolithic Integrated Circuit (MIMIC) phase 1 program, Contract no.

DAAL01-88-C-0835, Department of the Army, U.S. Army Electronics Technology and Devices Laboratory, Fort Monmouth, N.J. 07703.

## REFERENCES

- [1] T.N. Ton, T.H. Chen, G.S. Dow, K. Nakano, L.C.T. Liu, and J. Berenz, "A Q-Band Monolithic AlGaAs/GaAs HEMT CPW Downconverter", IEEE GaAs IC Symposium Digest, pp 185 - 188, New Orleans, La. October, 1990.

- [2] J. Berenz, M. LaCon, M. Aust, "44 GHz Monolithic HEMT Downconverter", IEEE GaAs IC Symposium Digest, pp 189 - 192, New Orleans, La. October, 1990.

- [3] P. Wallace, R. Michels, J. Bayruns, S.B. Christiansen, N. Scheinberg, J. Wang, R. Goyal and M. Patel, "A Low Cost High Performance MMIC Low Noise Downconverter for Direct Broadcast Satellite Reception", IEEE Monolithic Circuits Symposium Digest, pp 7 - 10, Dallas, Tx. May, 1990.